**RESEARCH ARTICLE**

**OPEN ACCESS**

# **Implementation Reconfigurable Architecture For Generic OFDM Modulator (Hybrid Modulator Architecture)**

# C Lakshmi Kanth

Deptof Ece, Vlsi & Embedded System, Bangalore Institute Of Technology, Bangalore, India

# ABSTRACT

Modern world's wireless communication is booming and it uses multiple carriers for modulations .OFDM is multi carrier modulation and utilized in many standards of wireless communication such as DAB, DVB, wireless LAN etc. Notable fact is that the OFDM frame structure of these wireless communication are similar , this OFDM frames consists of number of OFDM symbols following with synchronizing signal with different cyclic prefix and guard interval. This paper shows how to develop generic OFDM modulator through a novel reconfigurable architecture to meet different wireless communication standards. *Keywords-* Multi-carrier, synchronization, indexing.

**I.INTRODUCTION** An OFDM is a special case of multi carrier modulation and widely used in wireless communication. Because of this wide usage of Orthogonal Frequency Division Multiplexing (OFDM) modulation, many researchers all over the world are researching in many directions to make major difference in modern modulation techniques. Project present a generic modulator which adapts to all wireless communication by just changing cyclic prefix and guard interval parameters.

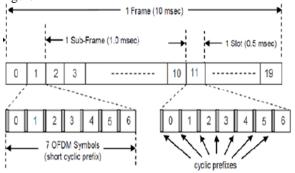

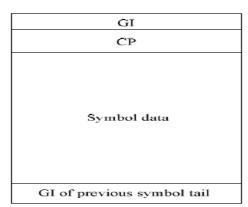

OFDM frames consist of number of OFDM symbols following with synchronizing signal with different cyclic prefix and guard interval. The structure of every single OFDM is as shown in figure

#### FIGURE1: OFDM FRAME STRUCTURE

This similarity in OFDM structure of all wireless communication makes my work of implementing reconfigurable architecture for generic OFDM modulator meaning full.

#### **II.BACKGROUND**

Table 1 shows OFDM parameters for DAB and 802.11A Wireless Standards.

**TABLE 1: OFDM PARAMETERS**

| Parameters | Standards               |          |  |  |  |

|------------|-------------------------|----------|--|--|--|

|            | Digital Audio           | 802.11a  |  |  |  |

|            | Broadcasting            |          |  |  |  |

|            | (Transmission Mode III) |          |  |  |  |

|            |                         |          |  |  |  |

| T(us)      | 0.48828125              | 0.05     |  |  |  |

| Tu(us)     | 125(256T)               | 3.2(64T) |  |  |  |

| Ts(us)     | 156(319T)               | 4(80T)   |  |  |  |

| Tg(us)     | 31(63T)                 | 0.8(16T) |  |  |  |

| Nv         | 192                     | 52       |  |  |  |

| Ns         | 256                     | 64       |  |  |  |

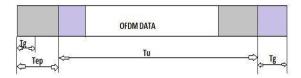

As depicted in table various timing parameters for standards like Digital Video Broadcasting (DAB), IEEE 802.11A are diverge. The structure of OFDM is below with timing contents.

FIGURE 2: OFDM timing parameters.

## **III.IMPLEMENTATION**

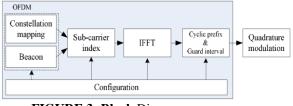

FIGURE 3: Block Diagram

### A.CONSTELLATION MAPPING

In this functional block depending on the type of modulation schemes (QPSK, 16qam, 64-qam and many more ) specified for the corresponding

www.ijera.com

network (DVB, DAB, wireless LAN and so on ) the constellation points are defined and the 16bit fixed point values of each corresponding constellation points are stored in the number of ROMs. The constellation mapping input is in the form of bit streams and then the incoming bits will be grouped according to the modulation scheme and then it is mapped to correct constellation symbols in according to the modulation method that is specified. The constellation points with their In-Phase and Quadrature-Phase values for each stated modulation schemes is stored in number of ROMs . Generally 16-bit fixed point data performs fine in many occasions. Figure 4 shows the constellation mapping.

FIGURE 4: Constellation Mapping

#### **B.BEACON**

Beacon is a pilot signal which is used for synchronization purpose. There are many challenging synchronization tasks to address from transmitter end to receiver end and beacon is also one of the signal used to achieve synchronization and it consists of an sequence generated by a specific formula.

#### C. IFFT

Currently, the concept of Software Defined Radio (SDR) is focused on flexibility on reconfiguration has been verified pretty efficient, and many IP cores are proposed by FPGA producer like Xilinx, ALTERA and many other companies. And to select a right IFFT block, certain aspects should be taken with more care and length and speed are the two main vital points of IFFT. In the complete design the length and speed of IFFT play an important role in describing how huge the bandwidth can be achieved. Thus the IFFT core should be taken on the basis of the bandwidth of system.

The IFFT length differs for different standards or different modes of a specific standard. An extra IFFT core can be used to give solution for this problem and this repetitive work will leads to wastage of resources. This describes how to use single IFFT for different size in applications of different network. It is usual that x (n) is divided into even and odd sequences. It is possible to achieve it is possible to achieve N-point IFFT from 2N-point IFFT by setting all odd indexed sequence to zeros and the first 128 outputs are considered as the output. Same like by placing input data on x (4n) where n ranges from 0, 1, (N/4)-1 N/2 points IFFT is achieved from 2N point IFFT and then the first quarter of the 2N point IFFT output is considered as the output for N/2 point IFFT.

The IFFT calculation can be done by using following equation

$$x(n) = \frac{1}{N} \left[ \sum_{k=0}^{N-1} X^*(k) W_N^{nk} \right]^{\frac{1}{2}}$$

The IFFT length differs in different standards or different modes of a specific standard. An extra IFFT core can be used to answer this problem; though, this repetitive work will leads to wastage of resources. Here described the way to use single IFFT for different length in different network applications.

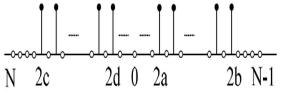

#### **D.SUB-CARRIER INDEX**

Sub-carrier indexing is previous part of IFFT computation as it has close relation with IFFT and it always has some null carriers with different positions. Even so the valid carriers are in order the starting and ending addresses of the active subcarriers can be located and saved in ROM. A counter that indicates the indices of the IFFT is generated and Sub-carrier will be allotted to the perfect position after correlating the counter value with the start and end addresses. Input symbols should be arranged by placing zeroes in their right positions.

The indices of IFFT get twice the amount because of inserted zeroes and the least significant bit of the counter will be neglected to avoid the alteration in the structure while correlating it with the marked points. Obviously, the lowest two bits should get empty when realizing N/2 points IFFT through 2N-point IFFT.

FIGURE 5: IFFT Input Using 2N-point IIFT.

## E. CYCLIC PREFIX AND GUARD INTERVALS

The lengths of cyclic prefix and guard interval are different for different network standards and the dual port RAM stores the output of the IFFT which is having maximum symbol length. Another vital role is to deliver the stored data in dual port RAM.

FIGURE 6: Cyclic Prefix and Guard Intervals

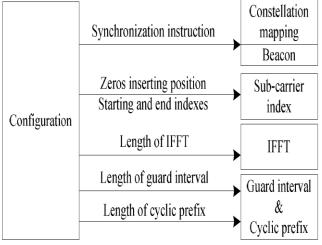

## F. CONFIGURATION

This part gives all the parameters related to the networks, including the option between ordinary signal and synchronizing signal, the position to which zeroes to be inserted, the indexes of the subcarriers, the IFFT length, guard interval and cyclic prefix. Figure 9 shows the exact parameters which are required to be configured.

FIGURE 7: Configuration Block

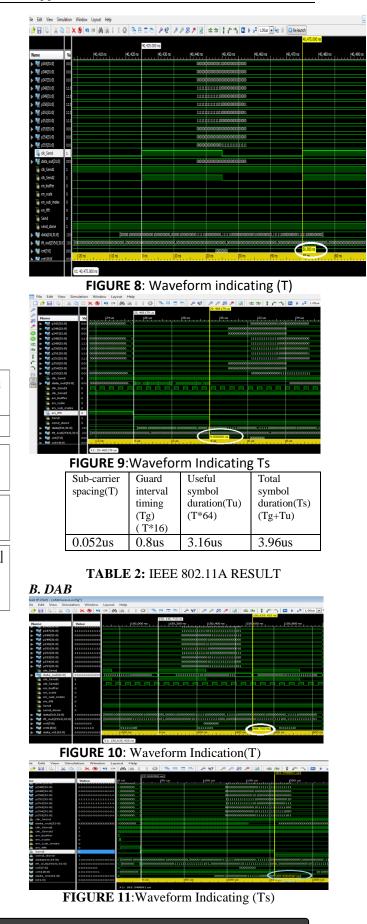

A. IEEE802.11A.

| Sub-<br>Carrier<br>spacing(<br>T) | Guard<br>interval<br>timing(Tg)<br>(T*64) | Useful<br>Symbol<br>duration(Tu<br>)<br>(T*256) | Total<br>duration(Ts)<br>(Tg+Tu) | Symbol |

|-----------------------------------|-------------------------------------------|-------------------------------------------------|----------------------------------|--------|

| 0.488<br>us                       | 31.68us                                   | 125.32u<br>s                                    | 156us                            |        |

## TABLE 3: DAB RESULT

#### V. CONCLUSION

In this paper, we enact, A Generalized Architecture for OFDM modulator in DAB, IEEE 802.11a, standards of wireless communication. Involving Quadrature Phase Shift Keying (QPSK) for Transmission Mode 3, respective to DAB, and simulated by Xilinx 14.2.Successful obtained Timing Parameters and verified with the theoretical timing parameters. Hence the complexity of using different Modulation Schemes for Different Kind of wireless Standards schemes is reduced

#### REFERENCES

- [1] Garaia,Rene Cumplido " On The Design Of FPGA Based OFDM Modulator For IEEE 802.11a." USA, IEEE, PP-3467,Sep 2010.

- [2] Mario PoggioniRugiini,Palo Banelli " A Novel simulation Model For Coded OFDM In Doppler Senario:DVB-T" ITALLY ,IEEE ,PP-033,Sep 2011.

- [3] Simen Li, Xio,Yun Chen "A Low Power 4K Point FFT Processor For CMMB OFDM Receiver" CHINA,IEEE,Vol-91,PP-387,July 2012.

- [4] Falio Da Casto,Pinto Fernandis,Ferndo Sergio Olivea,Scorlick Fabrico Publo Virgino " A Low Cost OFDM Based Modulation SchemsFor Data Communication In PassBand Frequency" BRAZIL,IEEE,PP-750,June-2013

- [5] Michal Merfenza, Chistopher Bobda "FPGA Implementation Of Sub-Carrier Index Modulation OFDM Tranreceiver ,USA ,IEEE ,PP-479, July 2013.

- [6] BeTU Zhang ,Xua Gua " A Novel Reconfigurable Architecture for generic OFDM Modulator Based On FPGA" CHINA,IEEE,March 2014.